当今时代,半导体行业的竞争可谓白热化,台积电、三星和英特尔等巨头都在争相展示3nm、2nm先进工艺的技术突破。这场超精细晶体管制造竞赛的背后,是对芯片工艺制程新时代的追逐,以及摩尔定律极限的挑战。

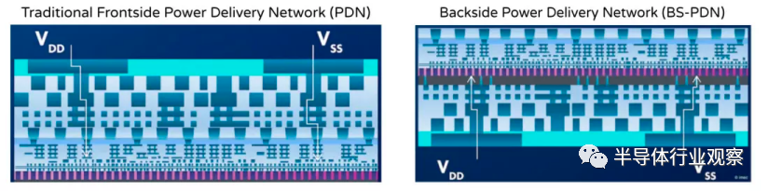

GAA、High-NA、先进封装等一系列创新技术,在为摩尔定律续命之余,越来越多的研究者近年来开始关注起一个新的技术方向——晶圆背面供电(Backside power delivery networks ,BSPDN)。

与EUV光刻机类似,BSPDN被视为继续开发更精细工艺节点技术的基本技术,预计将成为领先芯片晶圆厂的又一个竞争高地。

近日,韩国芯片巨头三星宣称要积极布局背面供电网络技术,并宣布将此导入逻辑芯片的开发蓝图。同时,英特尔、台积电等晶圆制造大厂也都在积极布局背面供电技术。

那么,受到业界大厂广泛追捧的背面供电技术是什么?将在摩尔定律中起到什么作用?

详解背面供电的优势与价值

过去多年来,芯片制造从最小的元件——晶体管开始,然后需要建立越来越小的线路层,用于连接晶体管与金属层,这些线路被称为信号互连线,当中还包括给晶体管供电的电源线。当芯片的裸片制造完成后,还需要把它翻转并封装起来对裸片进行保护,并提供了与外部的接口,使其真正成为一个商用化的芯片。

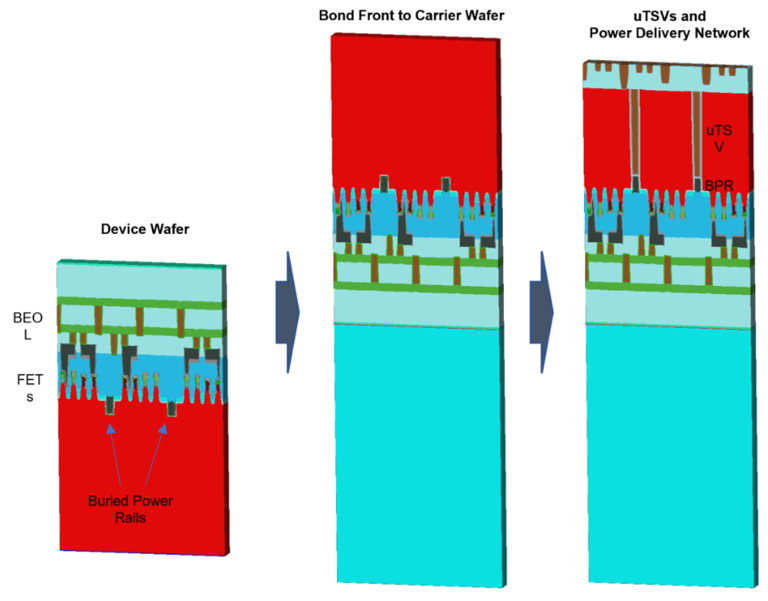

然而,随着摩尔定律的演进,晶体管越来越小,密度越来越高,堆栈层数也越来越多,可能需要穿过10-20层堆栈才能为下方的晶体管提供供电和数据信号,导致互连线和电源线共存的线路层变成了一个越来越混乱的网络。同时,电子在向下传输的过程中,会出现IR压降现象,导致电力损失产生。

除了电力损失之外,PDN占用的空间也是一个问题。如今芯片内部的电源线路,在布线复杂的后段制程上,往往占据了至少20%的绕线资源,如何解决信号网络跟供电网络之间的资源排挤问题,使元件进一步微缩,变成芯片设计者所面临的主要挑战之一。

对此,业界开始探索把供电网络转移到芯片背面的可能性。

背面供电技术(BSPDN)将原先和晶体管一同排布的供电网络直接转移到晶体管的背面重新排布,也是晶体管三维结构上的一种创新,该技术可以在增加单位面积内晶体管密度的同时,避免晶体管和电源网络之间的信号干扰,减轻线路后端的布线拥塞并提供电源性能优势,增强芯片的可靠性。

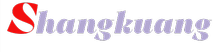

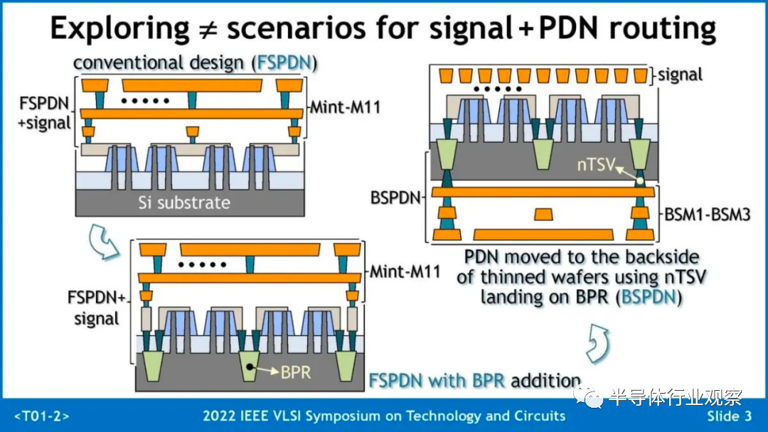

背部供电技术是一项应用于先进半导体的创新技术,旨在更好地挖掘晶圆背面空间的潜力。但要把PDN从芯片正面转移到背面,需要两项关键技术,分别是埋入式电源轨(BPR)与纳米硅穿孔(nTSV),

晶圆制造过程将先制造正面的晶体管,然后添加互联层,然后将晶圆反转,并对背面进行打磨减薄,在通过纳米硅穿孔(TSV)技术在晶圆背面进行制造供电网络,并与埋入式的电源轨连接。

其中,埋入式电源轨是一种微缩化技术,可以进一步降低标准单元的高度,并减缓IR压降问题。这些电源轨是埋在电晶体下方的导线,一部份藏在硅基板内,另一部份则在浅沟槽隔离氧化层内。它们取代了传统后段制程在标准单元布下的电源线与接地线。

使用埋入式电源轨进行背面供电

在2019年的IEEE国际电子研究会议上,IMEC携手Arm预测背面供电技术所能带来的效能升级。Arm在其开发与采用先进设计规则的CPU上进行模拟,并比较“传统供电”、“晶圆正面供电结合埋入式电源轨”、“背面供电搭配纳米硅穿孔与埋入式电源轨”这三种供电网络方法的优劣。

Arm研究人员发现BPR本身可以构建一个比普通前端供电网络效率高40%的电力网络。就供电效率的结果来看,第三种明显胜过其它方法,与传统的正面供电网络相比,芯片电压损耗大幅下降7倍。

总结来看,背面供电技术将带来截然不同的芯片性能提升:

-

改善物理设计。背面供电可以大幅减少DRC违规和时序拥堵,提高芯片利用率达85%以上。

-

金属线长缩减。背面供电在M1-M3层可实现30-50%的金属线长缩减,这将转化为时钟功耗降低、缓冲器数量减少和主动功耗降低。

-

IR Droop效应显著下降。背面供电可以实现更低的电源网格密度,IR降从50mV下降到20mV,大幅改善芯片性能。

-

系统级指标提升。线长减少和IR降低将带来时钟功耗减少15-20%、面积缩减15%的系统级优势。据称,与传统供电技术(FSPDN)相比,BSPDN的性能提高了44%,能效提高了30%。

-

成本降低。通过将电源分配到背面,下面的金属层将形成一个更宽松的间距,这意味着可以减少EUV光刻次数,降低成本。

诸多优势加持下,使背面供电成为了当前热门的技术议题。

代工三巨头,加码背面供电技术

台积电、三星、英特尔等芯片大厂都在积极布局背面供电网络技术,并宣布将导入先进逻辑芯片的开发蓝图。

三星BSPDN开发计划曝光

除了率先向GAA晶体管的转型外,背面供电技术也是三星追逐先进制程的一个杀手锏。

据ETNews报道,三星电子代工部门首席技术官Jung Ki-tae Jung在最近举办的论坛上宣布“我们计划在2027年将BSPDN应用于1.4nm工艺”。

根据TheElec和三星在今年VLSI研讨会上的演讲报告,与传统的前端供电网络相比,新的背面供电网络(BSPDN)方法成功地将所需的晶圆面积减少了14.8%,芯片能拥有更多空间,公司可增加更多晶体管,提高整体性能;同时布线长度减少了9.2%,有助于降低电阻、使更多电流通过,从而降低功耗,改善功率传输状况。

三星电子相关人士表示:“采用背面供电技术的半导体的量产时间可能会根据客户的日程安排而改变。”三星电子目标是在2025年量产2nm工艺,先于1.4nm工艺。据称,三星目前正在对背面供电技术的应用进行客户需求调查。

英特尔先声夺人

三星并非第一家要采用背面供电技术的芯片厂商。

英特尔显然也看到了背面供电技术带来的诸多好处,在BSPDN技术上的推进最为积极。

英特尔将自家的BSPDN称为PowerVia。不久前,英特尔发文介绍了PowerVia背面供电技术,该技术可帮助实现降低功耗、提升效率和性能,满足不断增长的算力需求。此外,背面供电技术也提高了设计的简易性。

在2023年VLSI研讨会上,英特尔展示了制造和测试其背面供电解决方案PowerVia的过程,并公布已经有良好性能的测试结果。据介绍,电源线原本可能占据芯片上面20%的空间,但是PowerVia背面供电技术节省了这一空间,也意味着互连层可以变得更宽松一些。

据了解,英特尔团队还特地制作了“Blue Sky Creek”测试芯片来证明这种方法,证明通过背面供电技术,电源线和互连线可以分离开来,并做得线径更大,以同时改善供电和信号传输。

测试结果显示,芯片大部分区域的标准单元利用率都超过90%,平台电压降低了30%,并实现了6%的频率增益,同时单元密度也大幅增加,并有望降低成本。PowerVia测试芯片也展示了良好的散热特性,符合逻辑微缩预期将实现的更高功率密度。

作为大幅领先竞争对手的背面供电解决方案,PowerVia让包含英特尔代工服务(IFS)客户在内的芯片设计公司能更快地实现产品能效和性能的提升。

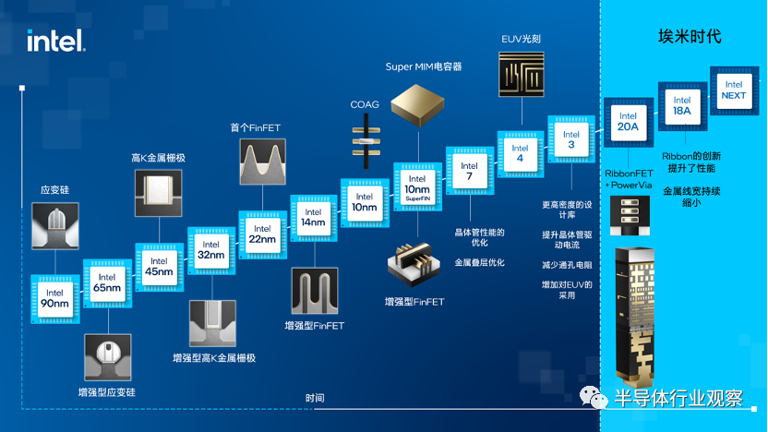

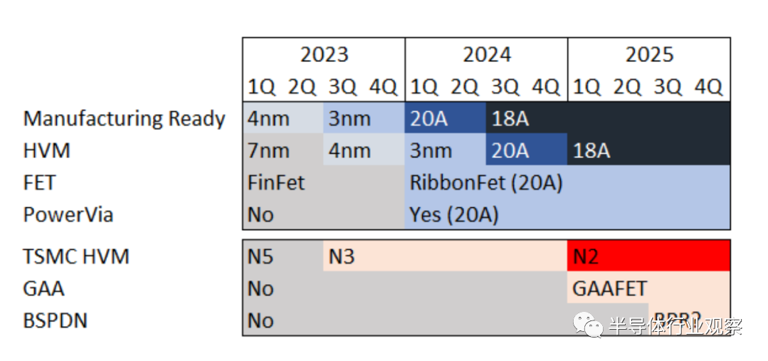

根据英特尔PowerVia背面供电技术的官方介绍,英特尔将在Intel 20A(2nm)将是英特尔首个采用PowerVia背面供电技术及RibbonFET全环绕栅极晶体管(RibbonFET是英特尔对GAA晶体管的实现)的节点,预计将于 2024 年上半年实现生产准备就绪,应用于未来量产的客户端ARL平台,目前正在晶圆厂启动步进(First Stepping)。

英特尔制程工艺路线图(来源:英特尔)

这是Pat Gelsinger和英特尔对其架构的一次大胆尝试。对于英特尔来说,在台积电之前采用PowerVia,通过使用RibbonFET 来做到这一点。这或许是在先进工艺上重新夺回领先的机遇。

届时,英特尔在芯片设计和制程技术创新方面或将处于行业领先地位。

台积电略显保守

相对于英特尔来说,台积电对BSPDN技术的应用更加保守。台积电选择的BSPDN实现方法是一种低复杂度的埋入式电源轨,这种技术成功率比较高,因为可以在现有的工具上完成。

在台积电2023年技术研讨会上,其透露N2P制程将通过背面供电技术减少IR Drop和改善信号,将性能提高10%-12%,并将逻辑面积减少10%-15%。

但关于如何实施背面供电网络技术,台积电并没有过多的透露。但台积电曾经介绍过3D IC封装技术SoIC,这是他们实现背面供电的一个很重要的前提准备。

有市场消息称,台积电如期2025年上线2nm制程,2025年下半年在新竹市宝山乡量产,计划2026年推出N2P制程,这个制程将采用BSPDN技术。

背面供电优势明显,挑战仍在

虽然从FSPDN到BSPDN的转变听起来很有希望,且优势明显,但BSPDN距离真正商用还有一定距离。

真正的背面供电网络的实现伴随着额外的技术复杂性。一方面,背面供电技术需要一种专用的晶圆减薄工艺以及处理将器件晶圆背面电连接到正面的纳米硅通孔 (nTSV) 的能力。

另一方面,实现晶圆背面电源供应需要在晶圆背面添加金属层(背面电极),但背面电极的的加工和设计并不像正面那样简单,由于背面电极和正面电路之间存在物理和电学障碍,因此必须进行详细的物理和电学模拟和设计。

此外,背面供电技术还存在调试、散热和设计等方面的技术挑战。

调试和检查是BSPDN最有趣的问题之一。英特尔称其为“黑天鹅”事件,因为调试的许多工具都必须从头开始创建,所有调试工具和EDA设计工具都是为前端设计而设计的。相关厂商不仅要弄清楚如何生产该工艺,还要弄清楚如何扩展该工艺。

热管理是另一个巨大的挑战,温度是人们对背面电源一直担心的问题之一,因为晶体管的埋层将更难冷却,而且层数越多,问题就越多。

三星在研讨会上还提出了实施背面供电传输模型的最大挑战之一,即与BSPDN相关的拉伸强度可能会降低。在实际应用时,BSPDN可以减少拉应力作用和硅通孔电极(TSV),导致与金属层分离。

三星表示,这个问题可以通过降低高度或加宽TSV来解决,但在正式宣布解决方案之前需要进行详细的研究和测试。要成功应用BSPDN技术,还需要在信号和电力线连接方面取得更多进步。除了上述之外,还需要在化学机械抛光 (CMP) 技术方面取得进步,当前的CMP实施用于从晶圆背面去除5-10微米的“峰谷”,而实施BSPDN可能需要一种新的方法来抛光晶圆而不损坏底层功率元件。

写在最后

背面供电技术的出现,成为了在下一代光刻机出现之前延续摩尔定律的一大关键,芯片突破3nm/2nm的关键技术之一。

不难发现,背面供电网络技术已成为过去几年在整个芯片制造行业悄然发展的技术概念,预计未来所有领先的芯片晶圆厂都将转向该技术。

从目前各企业进展和投入力度来看,英特尔正在领衔出击,三星和台积电则进度稍慢。

如果英特尔因为没有更早使用EUV 失去了对台积电的领先优势,那么台积电也可能会因为没采取积极的设计举措来提高性能而失去领先优势。随着三星的加入,三家在先进制程上竞争的代工厂全部加入了BSPDN的研究,这也意味着BSPDN可能会成为一个巨大的拐点。

除了晶圆制造公司,上游的设备公司也在BSPDN领域展开了研究。应用材料公司与BESI合作推出的Die-to-Wafer工具,Tokyo Electron提供了一种新Wafer to Wafer工具。这些市场是巨大的增量增长驱动力,背面供电布线的设备预计将以现在晶圆制造的设备3倍的增长速度增长。

总体而言,BSPDN技术的应用将推动半导体工艺的进一步发展,为行业带来更高的效率和性能。英特尔、三星电子、台积电,以及产业链企业等都在不断努力寻求技术突破,以保持在竞争激烈的半导体市场中的领先地位。随着时间的推移,我们期待看到更多关于BSPDN技术的进展和应用。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。